Pengenalan cip pemacu LED

dengan perkembangan pesat industri elektronik automotif, cip pemacu LED berketumpatan tinggi dengan julat voltan input yang luas digunakan secara meluas dalam pencahayaan automotif, termasuk lampu depan dan belakang luaran, lampu dalaman dan lampu latar paparan.

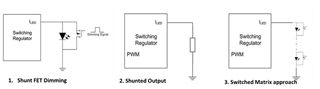

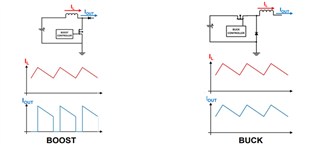

Cip pemacu LED boleh dibahagikan kepada peredupan analog dan peredupan PWM mengikut kaedah peredupan.Peredupan analog agak mudah, peredupan PWM agak kompleks, tetapi julat peredupan linear lebih besar daripada peredupan analog.Cip pemacu LED sebagai kelas cip pengurusan kuasa, topologinya terutamanya Buck dan Boost.arus keluaran litar buck berterusan supaya riak arus keluarannya lebih kecil, memerlukan kapasiti keluaran yang lebih kecil, lebih kondusif untuk mencapai ketumpatan kuasa tinggi litar.

Rajah 1 Output Current Boost vs Buck

Rajah 1 Output Current Boost vs Buck

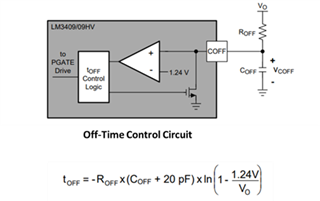

Mod kawalan biasa bagi cip pemacu LED ialah mod semasa (CM), mod COFT (masa MATI terkawal), mod COFT & PCM (mod semasa puncak).Berbanding dengan kawalan mod semasa, mod kawalan COFT tidak memerlukan pampasan gelung, yang kondusif untuk meningkatkan ketumpatan kuasa, sambil mempunyai tindak balas dinamik yang lebih pantas.

Tidak seperti mod kawalan lain, cip mod kawalan COFT mempunyai pin COFF yang berasingan untuk tetapan luar masa.Artikel ini memperkenalkan konfigurasi dan langkah berjaga-jaga untuk litar luaran COFF berdasarkan cip pemacu LED Buck dikawal COFT biasa.

Konfigurasi asas COFF dan langkah berjaga-jaga

Prinsip kawalan mod COFT ialah apabila arus induktor mencapai paras arus set off, tiub atas dimatikan dan tiub bawah dihidupkan.Apabila masa mematikan mencecah kepada MATI, tiub atas dihidupkan semula.Selepas tiub atas dimatikan, ia akan kekal padam untuk masa yang tetap (tOFF).tOFF ditetapkan oleh kapasitor (COFF) dan voltan keluaran (Vo) di pinggir litar.Ini ditunjukkan dalam Rajah 2. Oleh kerana ILED dikawal ketat, Vo akan kekal hampir malar pada julat luas voltan dan suhu input, menghasilkan tOFF yang hampir malar, yang boleh dikira menggunakan Vo.

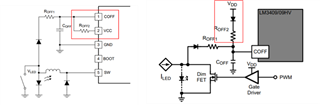

Rajah 2. litar kawalan masa off dan formula pengiraan tOFF

Rajah 2. litar kawalan masa off dan formula pengiraan tOFF

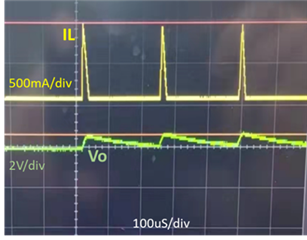

Perlu diingatkan bahawa apabila kaedah peredupan yang dipilih atau litar peredupan memerlukan keluaran yang dipendekkan, litar tidak akan bermula dengan betul pada masa ini.Pada masa ini, riak arus induktor menjadi besar, voltan keluaran menjadi sangat rendah, jauh lebih rendah daripada voltan yang ditetapkan.Apabila kegagalan ini berlaku, arus induktor akan berfungsi dengan masa mati maksimum.Biasanya masa rehat maksimum yang ditetapkan di dalam cip mencapai 200us~300us.Pada masa ini arus induktor dan voltan keluaran nampaknya memasuki mod cegukan dan tidak dapat mengeluarkan secara normal.Rajah 3 menunjukkan bentuk gelombang yang tidak normal bagi arus induktor dan voltan keluaran TPS92515-Q1 apabila perintang shunt digunakan untuk beban.

Rajah 4 menunjukkan tiga jenis litar yang boleh menyebabkan kerosakan di atas.Apabila FET shunt digunakan untuk memalapkan, perintang shunt dipilih untuk beban, dan beban adalah litar matriks pensuisan LED, kesemuanya mungkin memendekkan voltan keluaran dan menghalang permulaan biasa.

Rajah 3 TPS92515-Q1 Arus dan Voltan Keluaran Induktor (Kerosakan Pendek Output Beban Perintang)

Rajah 3 TPS92515-Q1 Arus dan Voltan Keluaran Induktor (Kerosakan Pendek Output Beban Perintang)

Rajah 4. Litar yang boleh menyebabkan pintasan keluaran

Untuk mengelakkan ini, walaupun output dipintas, voltan tambahan masih diperlukan untuk mengecas COFF.Bekalan selari yang VCC/VDD boleh digunakan sebagai mengecas kapasitor COFF, mengekalkan masa mati yang stabil dan mengekalkan riak yang berterusan.Pelanggan boleh menempah perintang ROFF2 antara VCC/VDD dan COFF apabila mereka bentuk litar, seperti yang ditunjukkan dalam Rajah 5, untuk memudahkan kerja penyahpepijatan nanti.Pada masa yang sama, lembaran data cip TI biasanya memberikan formula pengiraan ROFF2 khusus mengikut litar dalaman cip untuk memudahkan pemilihan perintang pelanggan.

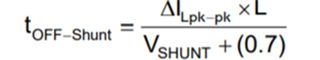

Rajah 5. Litar Penambahbaikan ROFF2 Luaran SHUNT FET

Rajah 5. Litar Penambahbaikan ROFF2 Luaran SHUNT FET

Mengambil kesalahan keluaran litar pintas TPS92515-Q1 dalam Rajah 3 sebagai contoh, kaedah yang diubah suai dalam Rajah 5 digunakan untuk menambah ROFF2 antara VCC dan COFF untuk mengecas COFF.

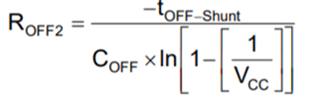

Memilih ROFF2 ialah proses dua langkah.Langkah pertama ialah mengira masa tutup yang diperlukan (tOFF-Shunt) apabila perintang shunt digunakan untuk output, di mana VSHUNT ialah voltan keluaran apabila perintang shunt digunakan untuk beban.

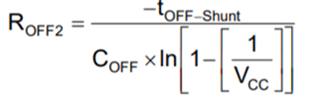

Langkah kedua ialah menggunakan tOFF-Shunt untuk mengira ROFF2, iaitu caj dari VCC ke COFF melalui ROFF2, dikira seperti berikut.

Langkah kedua ialah menggunakan tOFF-Shunt untuk mengira ROFF2, iaitu caj dari VCC ke COFF melalui ROFF2, dikira seperti berikut.

Berdasarkan pengiraan, pilih nilai ROFF2 yang sesuai (50k Ohm) dan sambungkan ROFF2 antara VCC dan COFF dalam kes kerosakan dalam Rajah 3, apabila output litar adalah normal.Juga ambil perhatian bahawa ROFF2 sepatutnya lebih besar daripada ROFF1;jika terlalu rendah, TPS92515-Q1 akan mengalami masalah masa hidup minimum, yang akan mengakibatkan peningkatan arus dan kemungkinan kerosakan pada peranti cip.

Berdasarkan pengiraan, pilih nilai ROFF2 yang sesuai (50k Ohm) dan sambungkan ROFF2 antara VCC dan COFF dalam kes kerosakan dalam Rajah 3, apabila output litar adalah normal.Juga ambil perhatian bahawa ROFF2 sepatutnya lebih besar daripada ROFF1;jika terlalu rendah, TPS92515-Q1 akan mengalami masalah masa hidup minimum, yang akan mengakibatkan peningkatan arus dan kemungkinan kerosakan pada peranti cip.

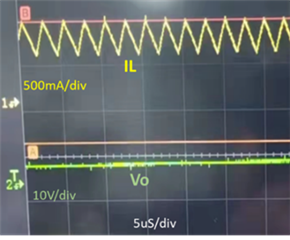

Rajah 6. Arus aruhan TPS92515-Q1 dan voltan keluaran (normal selepas menambah ROFF2)

Rajah 6. Arus aruhan TPS92515-Q1 dan voltan keluaran (normal selepas menambah ROFF2)

Masa siaran: Feb-15-2022